Latest Post

VLSI: 4 Bit Full Adder with Carry Select Structural/Gate Level Modelling with Testbench

- Get link

- X

- Other Apps

Verilog Code for 4 Bit Full Adder with Carry Select Structural/Gate Level Modelling

module FACS(

input [3:0]x,cin,

input [3:0]y,

output [3:0]s,

output cout,

wire c0,c1,c2,c3,c4,c5,c6,c7,a0,a1,a2,a3,a4,a5,a6,a7

);

//for carry '0'

fa f0(a0,c0,0,x[0],y[0]);

fa f1(a1,c1,c0,x[1],y[1]);

fa f2(a2,c2,c1,x[2],y[2]);

fa f3(a3,c3,c2,x[3],y[3]);

//for carry '1'

fa f4(a4,c4,1,x[0],y[0]);

fa f5(a5,c5,c4,x[1],y[1]);

fa f6(a6,c6,c5,x[2],y[2]);

fa f7(a7,c7,c6,x[3],y[3]);

//two:one MUX

mux m0(s[0],cin,a0,a4);

mux m1(s[1],cin,a1,a5);

mux m2(s[2],cin,a2,a6);

mux m3(s[3],cin,a3,a7);

mux m4(cout,cin,c7,c3);

endmodule

//full adder

module fa(sum,carry,a,b,c4);

output sum,carry;

input a,b,c4;

wire p,q,r;

xor(p,a,b);

and(r,a,b);

xor(sum,p,c4);

and(q,p,c4);

or(carry,q,r);

endmodule

//mux

module mux(

output Y,

input D0, D1, S,

wire T1, T2, Sbar

);

and (T1, D1, S), (T2, D0, Sbar);

not (Sbar, S);

or (Y, T1, T2);

endmodule

//Testbench code for Full Adder Structural/Gate Level Modelling

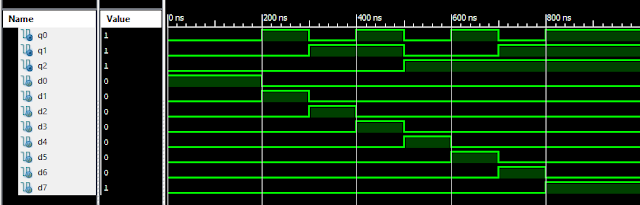

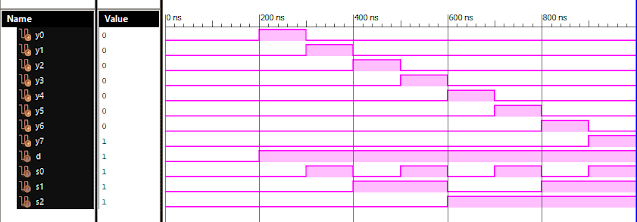

initial begin// Initialize Inputs

x = 0;y = 0;cin = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

#100;x = 0;y = 0;cin = 1;

#100;x = 0;y = 1;cin = 0;

#100;x = 0;y = 1;cin = 1;

#100;x = 1;y = 0;cin = 0;

#100;x = 1;y = 0;cin = 1;

#100;x = 1;y = 1;cin = 0;

#100;x = 1;y = 1;cin = 1;end

- Get link

- X

- Other Apps

Comments

Post a Comment