Latest Post

Space Facts: Part 9 - Quantum Fluctuations

- Get link

- X

- Other Apps

Have you heard of Quantum Fluctuations?

It's a part of Quantum Physics. Quantum Fluctuations describe that even from void space matter can be generated. But for this to happen there are certain rules:

1. Matter appearing from void will have negligible mass.

2. Matter will appear for very less time and disappear again.

3. Heavy mass matter cannot be generated.

Now, assume that in empty space there is no form of positive energy, but energy is present in negative form. From this negative energy particles may be formed for very less amount of time and gives back energy to surrounding and disappears.

By Quantum Fluctuations particles like electrons can be created but not protons and neutrons. Einstein compared this principle with universe and gave his theory of Relativity.

How we find the age of Universe practically?

BICEP 1 and BICEP 2 are gravity wave telescopes located in Antarctica. BICEP 2 captured 13.7 billion years old gravity waves, which were the oldest waves ever captured by any telescope.

To know what are gravity waves Click Here.

- Get link

- X

- Other Apps

Popular posts from this blog

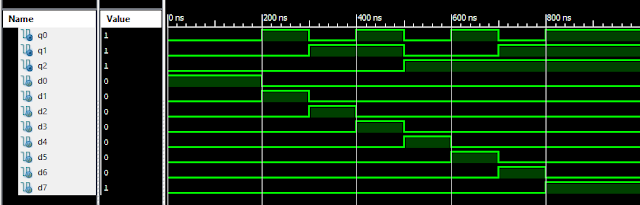

VLSI: 8-3 Encoder Dataflow Modelling with Testbench

Verilog Code for 8-3 Encoder Dataflow Modelling module encoder_8_to_3( input d0, input d1, input d2, input d3, input d4, input d5, input d6, input d7, output q0, output q1, output q2 ); assign q0 = ( d1 | d3 | d5 | d7 ); assign q1 = ( d2 | d3 | d6 | d7 ); assign q2 = ( d4 | d6 | d5 | d7 ); endmodule //Testbench code for 8-3 Encoder Dataflow Modelling initial begin ...

VLSI: 4-1 MUX Dataflow Modelling with Testbench

Verilog Code for 4-1 MUX Dataflow Modelling module m41(out, i0, i1, i2, i3, s0, s1); output out; input i0, i1, i2, i3, s0, s1; assign y0 = (i0 & (~s0) & (~s1)); assign y1 = (i1 & (~s0) & s1); assign y2 = (i2 & s0 & (~s1)); assign y3 = (i3 & s0 & s1); assign out = (y0 | y1 | y2 | y3); endmodule //Testbench code for 4-1 MUX Dataflow Modelling initial begin // Initialize Inputs a = 1;b = 0;c = 0;d = 0;s0 = 0;s1 = 0; ...

Samir Palnitkar Solution Manual Free Download PDF of Verilog HDL

This is a solution guide to the exercises of the book "The Solution Manual of the Verilog HDL: A Guide to Digital Design and Synthesis by Samir Palnitkar". Following are the Solutions to Solution Manual on Verilog HDL: A Guide to Digital Design and Synthesis by Samir Palnitkar , exercises of all chapters in the book. Chapter 1 ----------------- No Exercises ---------------- Chapter 2 : Hierarchical Modeling Concepts Chapter 3 : Basic Concepts Chapter 4 : Modules and Ports Chapter 5: Gate-level Modeling Chapter 6 : Dataflow Modeling Chapter 7 : Behavioral Modeling Chapter 8 : Tasks and Functions Download Solution Manual: Click on this link (Mega.nz Link) [Solution Manual to Verilog HDL: A Guide to Digital Design and Synthesis by Samir Palnitkar] Preview of Solution Manual: For Verilog Programs: Go to Index of Verilog Programming Tags: Verilog HDL solutio...

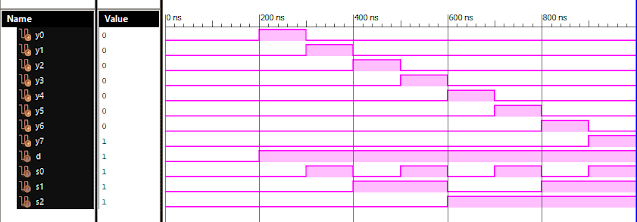

Verilog: 1to 8 DeMultiplexer (1-8 DEMUX) Dataflow Modelling with Testbench Code

Verilog Code for 1 to 8 DeMultiplexer Dataflow Modelling module demux_1_to_8( input d, input s0, input s1, input s2, output y0, output y1, output y2, output y3, output y4, output y5, output y6, output y7 ); assign s0n = ~ s0; assign s1n = ~ s1; assign s2n = ~ s2; assign y0 = d & s0n & s1n & s2n; assign y1 = d & s0 & s1n & s2n; assign y2 = d & s0n & s1 & s2n; assign y3 = d & s0 & s1 & s2n; assign y4 = d & s0n & s1n & s2; assign y5 = d & s0 & s1n & s2; assign y6 = d & s0n & s1 & s2; assign y7 = d & s0 & s1 & s2; endmodule //Testbench code for 1-8 DEMUX Dataflow Modelling initial begin // Initialize Inputs d = 0;s0 = 0;s1 = 0;s2 = 0; // Wait 100 ns for global reset to finish #100; // Add stimulus here #100; d = 1;s0 = 0;s1 = 0;s2 = 0; #100; d = 1;s0 = 1;s1 = 0;s2 = 0; #100; d = 1;s0 = 0;s1 = 1;s2 = 0; #100; d = 1;s0 = 1;s1 = 1;s2 = 0; #100; d = 1;s0 = 0;s1 = 0;s2 = 1; ...

VLSI: 1-4 DEMUX (Demultiplexer) Dataflow Modelling with Testbench

Verilog Code for 1-4 DEMUX Dataflow Modelling module demux_1_to_4( input d, input s0, input s1, output y0, output y1, output y2, output y3 ); assign s1n = ~ s1; assign s0n = ~ s0; assign y0 = d& s0n & s1n; assign y1 = d & s0 & s1n; assign y2 = d & s0n & s1; assign y3 = d & s0 & s1; endmodule //Testbench code for 1-4 DEMUX Dataflow Modelling initial begin // Initialize Inputs ...

Comments

Post a Comment