Latest Post

Verilog: NOR Gate Behavioral Modelling with Testbench Code

- Get link

- X

- Other Apps

Verilog Code NOR Gate Behavioral Modelling

module NOR_GATE (

input a, b,

output out );

reg out;

always @(a or b)

begin

if(a==0 & b==0)

out = 1’b1;

else

out = 1’b0;

endmodule

//test-bench

initial begin

a=0; b=0;

#100; //wait 100ns for global reset to finish

//add stimulus here

#100 a=0; b=1;

#100 a=1; b=0;

#100 a=1; b=1;

end

initial begin

#100 $monitor(“a=%b, b=%b, out=%b”, a, b, out);

end

endmodule

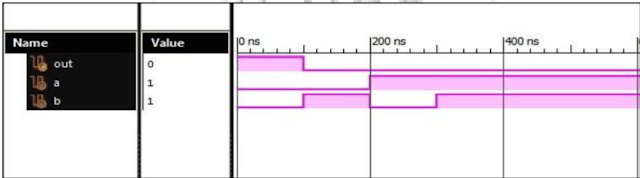

Xilinx Output:

- Get link

- X

- Other Apps

Comments

Post a Comment